实验2 组合逻辑电路部件实验

实验目的

掌握逻辑电路设计的基本方法

掌握EDA工具MAX-PlusII的原理图输入方法

掌握MAX-PlusII的逻辑电路编译、波形仿真的方法

输入设计的电路图;建立相应仿真波形文件,并进行波形仿真

记录波形和输入与输出的时延差;分析设计电路的正确性

3-8 译码器

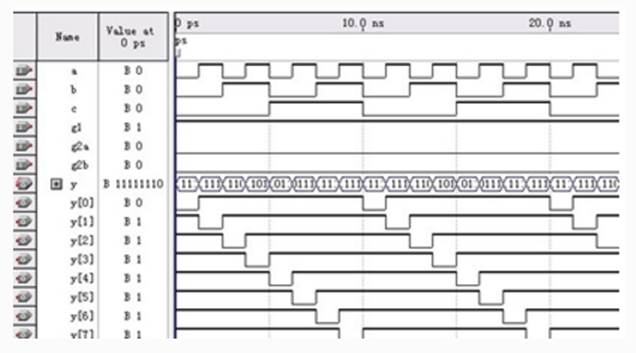

波形图

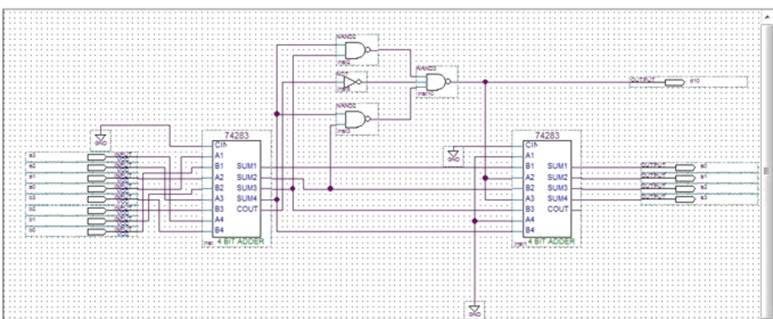

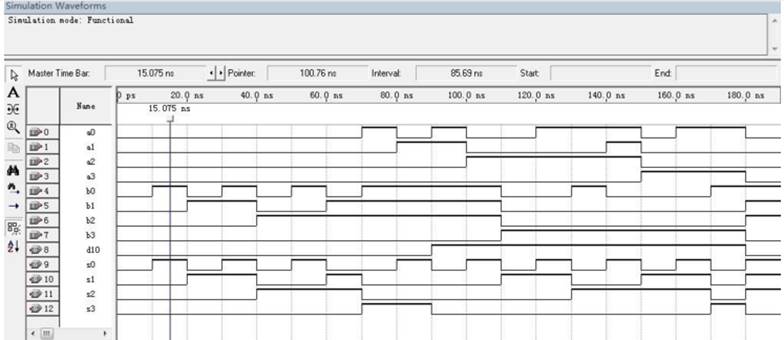

4位二进制加法器

实验内容:用D触发器实现4位二进制加法器,用仿真软件仿真,观察波形图

实验仪器:D触发器

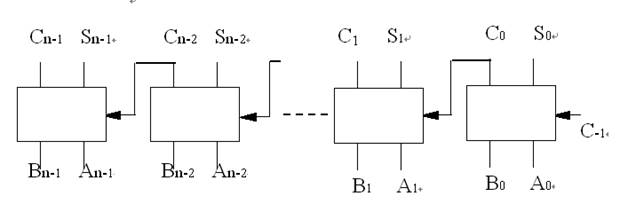

图中A和B是用来相加的两n位输入信号,Cn-1,Sn-1,Sn-2,……S2,S1,S0是它们的和。

在该电路中对A0和B0相加是用一个半加器,对其它位都用全加器。

如果需要串接这些电路以增加相加的位数,那么它的第一级也必须是一个全加器。

利用1位二进制全加器构成一个4位二进制全加器

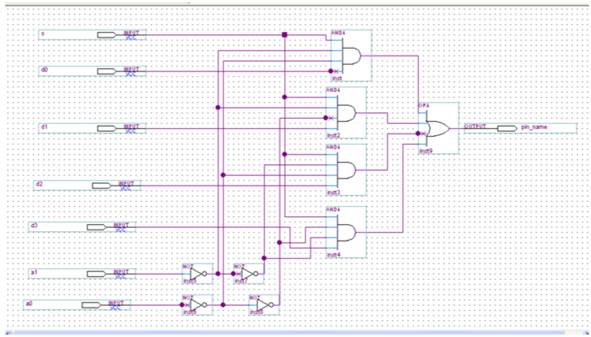

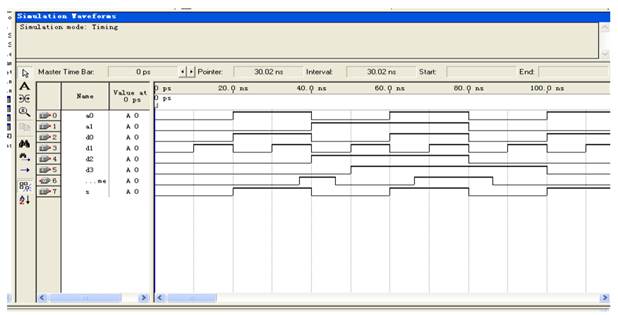

四选一数据选择器

实验内容:用与门、或门、非门设计四选一数据选择器,用仿真软件仿真,观察波形图

实验仪器:与门、或门、非门

数据选择器又称输入多路选择器、多路开关。它的功能是在选择信号的控制下,

从若干路输入数据中选择某一路输入数据作为输出。

实验3 时序电路设计

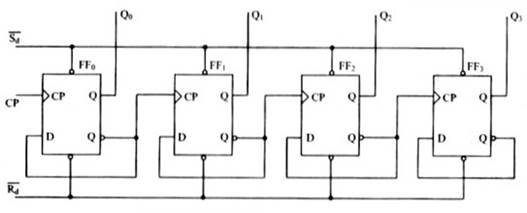

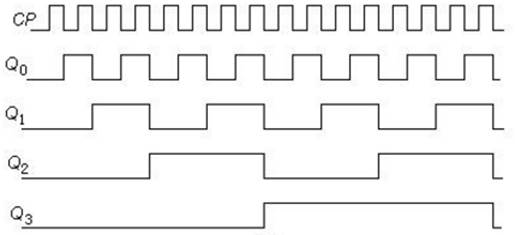

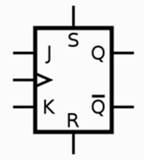

D触发器、JK触发器

实验目的:

1.掌握D触发器、JK触发器的工作原理。

2.学会正确使用D触发器、JK触发器。

3.学习利用EDA工具设计简单时序电路。

4.掌握简单时序电路的分析、设计、波形仿真、器件编程及测试方法

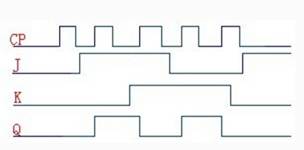

JK触发器JKFF(或双JK触发器74LS73、74LS76中一个JK触发器)功能测试与分析。

JK触发器输入端口CLR是复位端,PRN是置位端,CLKS是时钟。给出CK,J,K的波形,

仿真JK触发器的功能,说明JK触发器的CLK何时有效。

D触发器74LS74是上升沿触发,JK触发器74LS73是下降沿触发

JK触发器波形图

JK触发器波形图

D触发器DFF(或双D触发器74LS74中一个D触发器)功能测试。

D触发器的输入端口CLR是复位或清零,PRN是(置位);给定D(数据)、CLK(时钟)波形序列,

进行波形仿真,记录输入与输出Q波形。说明D触发器是电平触发还是上升沿触发,分析原因。

实验4基于VHDL的基本逻辑电路设计

实验目的:

学会使用VHDL语言设计数字单元电路的方法。

掌握用VHDL语言设计的数字单元电路的调试,波形仿真的方法。

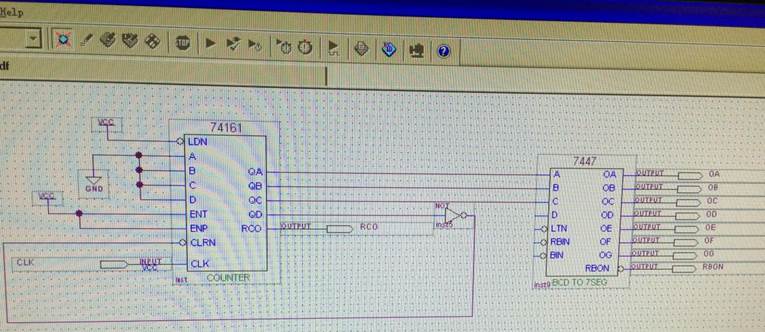

BCD码加法器

波形图

实验五 数字钟设计

实验目的:利用实验系统的资源,对设计的电路进行组装和功能检测。

设计一个四兆分频器,十进制计数器,BCD-7段译码器,利用实验系统的资源,

对设计的电路进行组装和功能检测。

10秒计时器

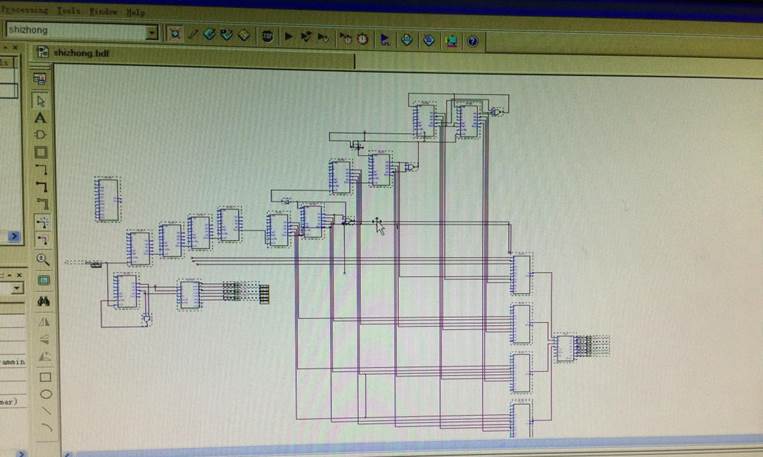

数字钟

实验目的:充分利用实验系统提供的硬件资源,用VHDL语言(或组合逻辑图像结合)

设计一个分(两位)、秒(两位)计时器。

包括分频器、变速部分、降速部分、数据选择部分、数字显示部分

写在最后

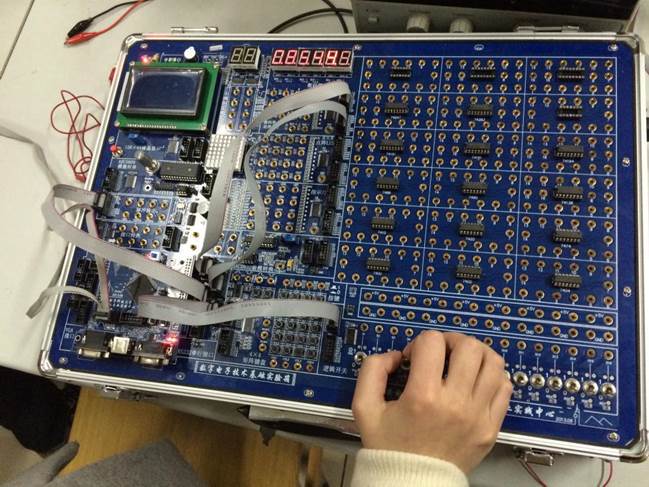

最近在整理以前做过的东西,现在看来基本什么都不记得了,只记得最后一张图里不是我的手,应该是位女同学的,当时互相偷,就硬偷...进行实验的电脑上都带着病毒,然后大家拷贝回来的PPT沾满了毒hhh,回来插自己电脑上很多都中招了...20200331_2302,我刚把那个PPT文件夹给删除了嘻嘻。

本科这四年的时光好快,现在很是感慨。